Introduction

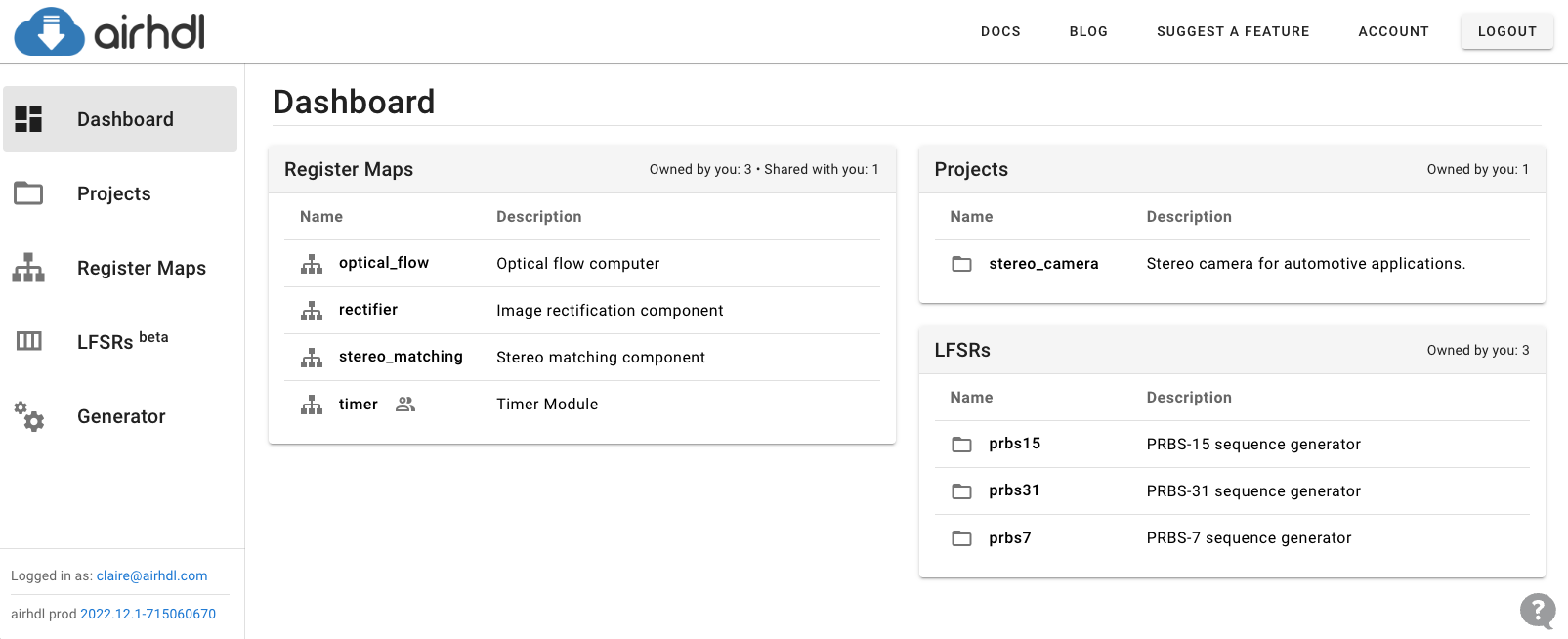

Welcome to airhdl, the web-based AXI4 VHDL and SystemVerilog register generator. Unlike traditional EDA tools, which often come with awkward user interfaces, high costs and complicated licensing mechanisms, airhdl offers a straightforward and easy-to-use way to manage register maps for your FPGA and SoC projects.

Creating a register map in airhdl is just a matter of firing up a web browser, logging in to airhdl.com, and entering your register definitions in our easy-to-use graphical user interface.

Comprehensive built-in design rule checks, which are executed automatically before any code generation, ensure that your register maps do not contain issues such as invalid or duplicated identifiers, or overlapping registers or fields.

For every register map that you create in airhdl, you have immediate access to a comprehensive set of generated files via the download button:

- C/C++ header

- SystemVerilog RTL (module and package)

- SystemVerilog testbench

- VHDL RTL (component and package)

- VHDL testbench

- HTML documentation

- Markdown documentation

- IP-XACT XML

- JSON object

Downloading the SystemVerilog and VHDL testbenches, as well as the IP-XACT XML, requires a Professional subscription.

Subscribers to the Professional CL plan can download the airhdl command-line generator, which allows them to generate all the files locally on their computer or build server. They can also upload register maps as JSON files for easy synchronization of local changes with the airhdl database.

Behind the scenes, airhdl keeps track of the changes you make to your register maps. Every time a register map is updated, airhdl automatically increments the register map’s revision number, which is included in every generated file. By comparing revision numbers, it's easy to check that your local files all correspond to the same register map revision.

Finally, subscribers to our Professional plans can share register maps with other airhdl users, such as team members or external partners, for easy collaboration. Welcome to a new EDA experience!